Hvordan kjøre LVS i Layout XL

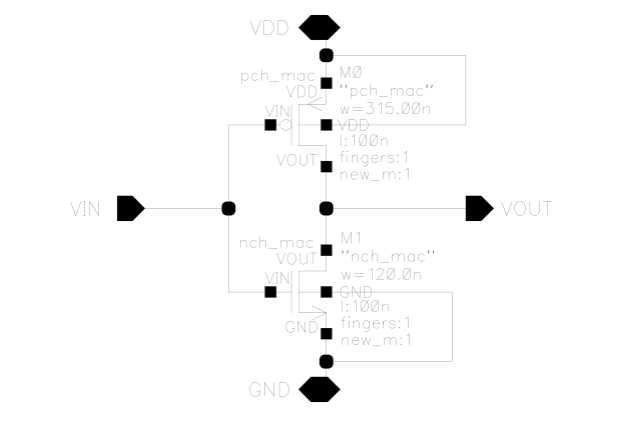

Det anbefales ikke å bruke symbolene gnd og vdd, bruk heller pinner av typen InputOutput med navn GND og VDD. Bruker du et annet navn må du fortelle cadence at det er henholdvis power og ground. Figuren under viser en korrekt skjematikk for en inverter.

Etter å ha kjørt DRC og blitt kvitt alle feilmeldinger kan man gå videre til LVS, denne sjekker at skjema og utlegg stemmer overens.

-

1. Legg til Pinner. I layout XL: Create -> Pin...

Terminal Names: Skriv inn “VDD GND”, velg inputOutput. Kryss av for “Display Pin Name” og trykke på “Display Pin Name Option...”. Velg en litt mer sakelig høyde, f.eks 0.2. Velg layer “M1 pn”, hvis pinnen ligger i metall 1. Har du kontakt i et høyere metalllag (si metall 2) velger man “M2 pn” osv. Pinnen VDD og GND kan nå plasseres ut, pass på at teksten ligger innenfor pinnen. Altså: Navnet på pinnen må plasseres på selve pinnen og må være av samme lag som pinnen selv.

-

2. Legg til de andre pinnen i designet på samme måte, husk å velg riktig I/O type. Altså input for innganger og output for utganger.

-

3. Calibre -> “Run LVS”, under Rules velg LVS Rules File til “Calibre/lvs/calibre.lvs”

Under Inputs -> Netlist, huk av for “Export from schematic viewer”

-

4. Trykk Run LVS. Forhåpentligvis får du nå et smilefjes, hvis ikke har du enten gjort noe feil med pinnene (noe som er meget lett), eller koblet transistorene feil sammen. Husk at cadence skiller på source og drain, man kan snu på hva som er hva i properties for transistoren “Parameter -> S D swap”.